Fig. 4. A photograph of the FET structure in the coplanar waveguide environment.

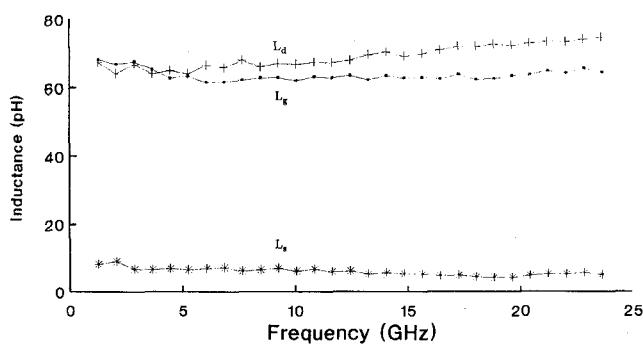

Fig. 5. Variation of the parasitic inductances with frequency.

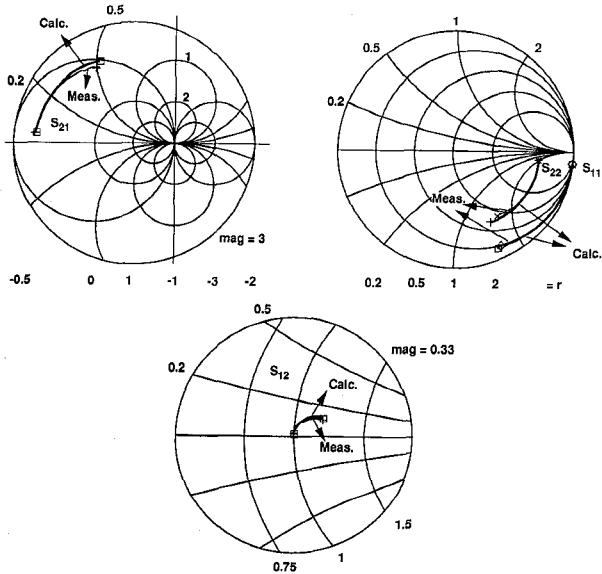

Fig. 6. Comparison of the measured and calculated  $S$ -parameters in the frequency range from 1.6 to 22.4 GHz. The calculations are based on the equivalent circuit element values extracted at 10.43 GHz.

The above technique and the equations given in [2] were used to calculate the small-signal equivalent circuit parameters of a pseudomorphic MODFET. The values of measured  $S$ -parameters under

“active” (“hot”) bias condition, and the variation of circuit elements with frequency are shown in Table I. Except for  $R_i$  and  $\tau$ , there is little variation with frequency. Extraction of  $R_i$  is difficult since it appears in series with the capacitor  $C_{gs}$ . The reactance of  $C_{gs}$ , at the frequencies of interest, could be two orders of magnitude larger than the resistance  $R_i$ . The value of  $\tau$  is also affected by the variations in  $R_i$ . In order to further investigate the influence of  $R_i$  on  $\tau$ , the value of  $R_i$  was set to zero  $R_i = 0.0$ . The values of  $\tau$  thus obtained ranged from 0.30–0.43 picoseconds for all the frequencies of Table I, except the first four which varied between 0.12 to 0.70 picoseconds. The polar plots of Fig. 6 show the measured  $S$ -parameters and those calculated based on the circuit element values of Table I at 10.43 GHz. Good agreement between the measured and calculated  $S$ -parameters is observed over the whole frequency range especially at lower frequencies.

## REFERENCES

- [1] G. Dambrine, A. Cappy, F. Heliodore, and E. Playez, “A new method for determining the FET small-signal equivalent circuit,” *IEEE Trans. Microwave Theory Tech.*, vol. 36, no. 7, pp. 1151–1159, July 1988.

- [2] M. Berroth and R. Bosch, “Broad-band determination of the FET small-signal equivalent circuit,” *IEEE Trans. Microwave Theory Tech.*, vol. 38, no. 7, pp. 891–895, July 1990.

- [3] —, “High-frequency equivalent circuit of GaAs FET’s for large-signal applications,” *IEEE Trans. Microwave Theory Tech.*, vol. 39, no. 2, pp. 224–229, Feb. 1991.

- [4] K. W. Lee, K. Lee, M. S. Shur, T. T. Vu, P. C. T. Roberts, and M. J. Helix, “Source, drain, and gate series resistances and electron saturation velocity in ion-implanted GaAs FET’s,” *IEEE Trans. Electron Devices*, vol. ED-32, no. 5, pp. 987–991, May 1985.

- [5] H. Vickes, “Determination of intrinsic FET parameters using circuit partitioning approach,” *IEEE Trans. Microwave Theory Tech.*, vol. 39, no. 2, pp. 363–366, Feb. 1991.

## Microstrip Quarter-Wave High Voltage DC Block

Thomas E. Koscica

**Abstract**—A microstrip high voltage dc block is presented. Silicon rubber is used to insulate a quarter-wave coupler and the resulting effective dielectric constant and impedance are discussed. DC isolation up to 4500 V is achieved.

## I. INTRODUCTION

The need for dc blocks that can handle over several hundred volts can be grouped into two areas: First, the biasing of high voltage devices such as vacuum tubes, IMPATT devices, and electrooptic phase shifters. Second, the protection enhancement of bias tees and microwave equipment incorporating them.

Standard coupled line bias gaps, [1]–[4], have well developed microwave models with good performance for voltage supplies less than 200 V, depending on humidity. Above this bias level, attention must be given to voltage breakdown of either air or the dielectric of a lumped element capacitor where used.

Manuscript received December 30, 1991; revised May 12, 1991.

The author is with the U.S. Army, SLCET-MP, Fort Monmouth, NJ 07703-5601.

IEEE Log Number 9204011.

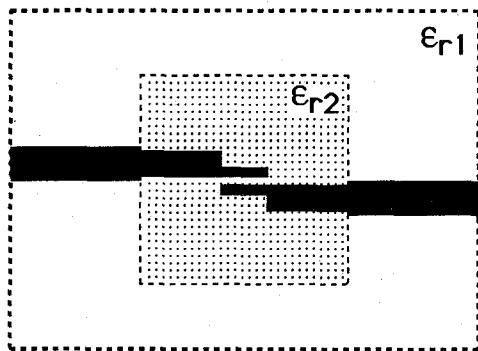

Fig. 1. Top and side views of high voltage bias gap showing high voltage insulator dielectric.

Recently a novel ground plane dc block for microstrip was introduced, [5], and subsequently extended, [6], to withstand voltages as high as 4 kV. Two issues limit its acceptance in high voltage applications: First, the present dependence on empirical data until a suitable modeling method is developed. Second, the long gap across which high voltage is applied; any processing flaw along this gap length results in reduced voltage breakdown protection.

The high voltage dc block discussed in this paper is shown in Fig. 1. It is based upon quarter wave coupled lines with the addition of a layer of silicon rubber to provide protection against voltage breakdown across the gap. As compared with the published microstrip high voltage dc block, [6], the design discussed in this paper features reduced complexity, need for single side processing only, increased breakdown voltage, increased reliability, and availability of a suitable modeling method. It is straightforward to extend the design principles to other substrates, insulating coatings, frequencies, and multicoupled line filters.

## II. ANALYSIS

The high voltage bias gap of Fig. 1 is similar in operation to a standard quarter wave dc block for microstrip. The microstrip dc block with dielectric overlay must be analyzed to determine how the silicon dielectric affects the even and odd mode impedances of the coupled lines. In order to achieve good bandwidth with low standing wave ratio (SWR), the gap separation,  $s$ , and coupled line width,  $w$ , need to be adjusted. Additionally, the overlay material changes the effective dielectric constant along the coupled lines. By using this effective dielectric constant, the length of the coupled line section can be adjusted in order to get the required center frequency.

First consider the section of transmission line immediately next to the coupled line region. This section is coated in order to insure that the coupled lines have a guard region of silicon rubber.

In order to get the effective dielectric constant of this overlay microstrip region, which is needed for appropriate transmission line impedance designs, the variational technique combined with the transverse transmission line method, [7], is used. This method generates values for  $C_{er}$ , the capacitance per unit length with the substrate and overlay dielectrics present as shown in Fig. 2, and  $C_{air}$ , the capacitance per unit length for both dielectrics replaced by air. In terms of these two values, the effective dielectric constant for the

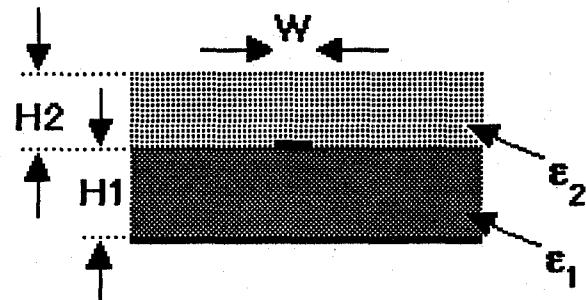

Fig. 2. Cross section of overlay microstrip.

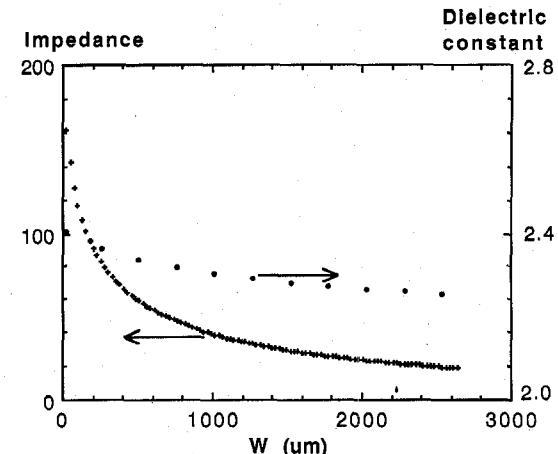

Fig. 3. Impedance and  $\epsilon_{eff}$  data for overlay microstrip with  $\epsilon_{r1} = 2.2$ ,  $\epsilon_{r2} = 2.7$ ,  $H1 = 254\mu\text{m}$ ,  $H2 = 2540\mu\text{m}$ .

overlay microstrip is [8]:

$$\epsilon_{eff} = \frac{C_{er}}{C_{air}}$$

Results for various metallization widths are shown in Fig. 3. One can get the impedance of the overlay microstrip line by using the following expression derived from [8]:

$$Z = \frac{1}{c_o \sqrt{\epsilon_{eff}} C_{air}}$$

where the value used for  $C_{air}$  is obtained from standard microstrip equations, [9], [10], using  $\epsilon_r = 1$ .

The next step in analyzing the high voltage gap is to determine the dimensions of the coupled lines.

A criteria for microwave design is that given the required SWR and bandwidth, the physical dimensions are determined. By using [12], SWR and bandwidth are mathematically related to  $Z_{oe}$  and  $Z_{oo}$ , the required even and odd mode impedances values for the coupled lines. From [12]:

$$Z_{oe} = \sqrt{S} \left[ 1 + \sqrt{1 + \frac{\sqrt{1 + \Omega_c^2}}{\Omega_c^2} \left( 1 - \frac{1}{S} \right)} \right]$$

$$Z_{oo} = \sqrt{S} \left[ -1 + \sqrt{1 + \frac{\sqrt{1 + \Omega_c^2}}{\Omega_c^2} \left( 1 - \frac{1}{S} \right)} \right]$$

where  $S$  is the standing wave ratio and  $\Omega_c$  is a normalized bandwidth as described in [12].

To relate the even and odd mode impedances to physical dimensions, the variational technique combined with the transverse transmission line method, [7], is used to obtain values for  $C_{er(\text{even})}$  and  $C_{er(\text{odd})}$ , the even and odd mode capacitances per unit length of

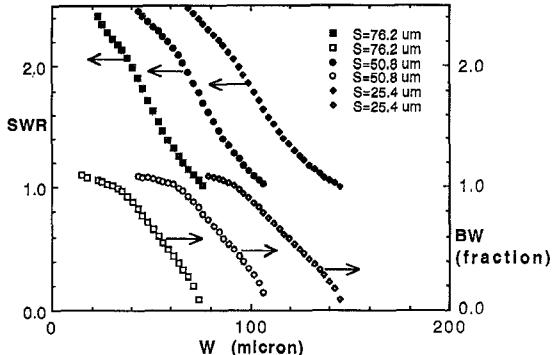

Fig. 4. Calculated SWR and bandwidth as functions of  $s$  and  $w$ .

the coupled lines with the dielectric overlay present, and  $C_{\text{air(odd)}}$  and  $C_{\text{air(even)}}$ , the capacitance per unit length with all dielectric replaced by air. Then the effective dielectric constants for the coupled lines are [8]:

$$\epsilon_{\text{eff(even)}} = \frac{C_{\text{er(even)}}}{C_{\text{air(even)}}}$$

$$\epsilon_{\text{eff(odd)}} = \frac{C_{\text{er(odd)}}}{C_{\text{air(odd)}}}$$

One can get the impedance on the etched dielectric microstrip line by using the following expression which can be easily derived from [8]:

$$Z_{oe} = \frac{1}{c_o \sqrt{\epsilon_{\text{eff(even)}}} C_{\text{air(even)}}}$$

$$Z_{oo} = \frac{1}{c_o \sqrt{\epsilon_{\text{eff(odd)}}} C_{\text{air(odd)}}}$$

The effective dielectric constant for the coupled lines becomes:

$$\epsilon_{\text{eff}} = \sqrt{\epsilon_{\text{eff(even)}} \epsilon_{\text{eff(odd)}}}$$

Computer calculations based on the above method result in obtaining SWR and bandwidth as functions of the gap width,  $s$ , and the coupled line width,  $w$ . Results are presented in Fig. 4.

The length of the coupled lines is slightly less than  $\lambda_g/4$  where  $\lambda_g$  is  $\lambda_o/\sqrt{\epsilon_{\text{eff}}}$  and  $\lambda_o$  is the wavelength in air at the center of the passband. The slight reduction is due to end effects since square discontinuities are used without compensation, [11].

### III. EXPERIMENTAL

Several circuits were constructed resulting in SWR and bandwidth values only slightly worse than predicted. Modeling for finite thickness conductors, as well as the use of a compensation curve similar to reference [11], are possible improvements. Both of these effects are not included in the basic analysis, [12]. Of interest here is that a duroid based circuit with  $s = 50\mu\text{m}$ ,  $w = 60\mu\text{m}$ , gave a voltage breakdown over 4500 V. When breakdown does occur, it is often at one of the open ends of the coupled lines. This occurs because of the increased dc electric field which occurs at these ends. Rounding the open ends of the coupled lines reduces the field stress at these points and suppresses this failure mode. By making the gap width larger, one can get increased voltage breakdown protection at a tradeoff of poorer SWR and bandwidth characteristics.

### IV. CONCLUSIONS

The three constraints on high voltage bias gap design using quarter wave coupled lines are SWR, bandwidth, and voltage breakdown. Since for a given substrate thickness only the gap width and coupled

line width can be varied, the problem is over constrained. It happens that typical gap separations used for achieving a required SWR and bandwidth result in sufficiently high voltage dc blocks; the over constraint is then not a problem of concern.

Breakdown voltages over 4500 V are routinely obtained by the method described in this paper. This represents an increased voltage protection capability in a circuit that has a form which can be modeled. These principles can easily be extended to many element coupled line filters to achieve any standard passband characteristic with improved high voltage protection.

### REFERENCES

- [1] D. Lacombe and J. Cohen, "Octave-band microstrip dc blocks," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-20, pp. 555-556, Aug. 1972.

- [2] B. A. Syrett, "A broad-band element for microstrip bias or tuning circuits," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-28, pp. 925-927, Aug. 1980.

- [3] S. R. Borgonkar and S. N. Rao, "Analysis and design of D.C. blocks," *Electron. Lett.*, vol. 17, pp. 101-103, Jan. 1981.

- [4] B. J. Minnis, "Printed circuit coupled-line filters for bandwidths up to and greater than an octave," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-29, pp. 215-222, Mar. 1981.

- [5] T. E. Koscica, "Wide-band ground-plane dc block and bias feed," *IEEE Trans. Microwave Theory Tech.*, vol. 38, pp. 805-806, 1990.

- [6] T. E. Koscica, "High voltage microwave dc block for microstrip ground planes," *Electron. Lett.*, vol. 26, pp. 1287-1288, 1990.

- [7] B. Bhat and S. K. Koul, "Unified approach to solve a class of strip and microstrip-like transmission lines," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-30, pp. 679-686, May 1982.

- [8] J. L. Klein, and K. Chang, "Optimum dielectric overlay thickness for equal even- and odd-mode phase velocities in coupled microstrip circuits," *Electron. Lett.*, pp. 274-276, Mar. 1990.

- [9] J. J. Lev, "Synthesize and analyze microstrip lines," *Microwaves and RF*, pp. 111-116, Jan. 1985.

- [10] M. Kirschning and R. H. Jansen, "Accurate model for effective dielectric constant of microstrip with validity up to millimeter-wave frequencies," *Electron. Lett.*, pp. 25-26, Feb. 1982.

- [11] D. Raicu, "Universal Taper for Compensation of Step Discontinuities in Microstrip lines," *IEEE Microwave Guided Wave Lett.*, vol. 1, pp. 249-251, Sept. 1991.

- [12] D. Kajfez and B. S. Vidula, "Design equations for symmetric microstrip dc blocks," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-28, pp. 974-981, Sept. 1980.